# Silicon Single Photon Avalanche Diodes for Quantum Key Distribution

S. Cova (1) (2), M. Ghioni(1) (2), I. Rech (1), A. Gulinatti (1), A. Giudice (2), P. Maccagnani (3) 1: Politecnico di Milano-DEI, p. Leonardo da Vinci 32, Milano I-20133 Italy, (cova@elet.polimi.it) 2: Micro-Photon-Devices MPD, via Stradivari 4, Bolzano I-39100 Italy 3: CNR-IMM, via Gobetti 101, Bologna I-40129 Italy

### **Abstract**

The progress in silicon planar device technologies has led single-photon avalanche diodes (SPAD) to emerge from the laboratory research phase and be commercially available from various manufactures. QKD systems can already exploit the available planar Si-SPAD devices, but they set strong demand for improved features and performance. A response can be given by new developments in a dedicated silicon planar technology. The present state of the art, the prospect and main issues will be discussed.

#### Introduction

In the past decade there has been growing interest in QKD systems operating at short wavelengths (< 1000 nm) [1, 2] due to the superior performance of technologically mature silicon single photon avalanche diodes (Si-SPADs). Si-SPADs with planar structure exhibit picosecond photon timing jitter and negligible afterpulsing effects, thus enabling quantum key distribution at GHz clock rates with sifted key rates over 1 Mbit/s. These devices find their main application in high-performance free-space [3] and fiber-based [4] QKD systems operating at 850 nm, although upconversion recently proved to be a viable solution for extending the operating range of planar Si-SPADs up to 1.55 µm wavelength [5, 6]. The prospect of widespread use of these detectors in QKD applications relies on the development of Si-SPADs with larger sensitive area diameter, improved photon detection efficiency (PDE) in the red and nearinfrared spectral range and shorter diffusion tail. In this paper, we describe our progress in improving the performance of planar Si-SPADs in order to meet such expectations.

# Advances in planar Si-SPAD technology

Planar Si-SPAD devices with thin depleted region (1-2 µm), fabricated in a standard CMOS silicon technology can attain time resolution down to less than 50 ps FWHM at room temperature [7]. Standard CMOS technology makes it possible to monolithically integrate the SPAD device and its associate quenching circuit, taking great advantage of reduced size and low parasitic capacitances. Unfortunately, the technologies available in industrial silicon foundries of CMOS circuits are not optimized for SPAD device fabrication, resulting in reduced photon detection efficiency (PDE) and relatively high dark count rate (DCR) and afterpulsing. So far, no CMOSbased SPAD devices with active area diameter > 100 um have been reported. To overcome these limitations we have developed a dedicated planar SPAD technology, achieving a reliable fabrication of high-performance devices with active area diameter up to 200 µm [8]. Efforts were mainly directed to:

- exploit specific gettering processes, as phosphorus diffusion and p/p+ segregation gettering for removing metal impurities from the detector active volume, therefore reducing DCR and afterpulsing effects;

- identify and remove or mitigate all the possible sources of contamination in the detector processing, with special care to transition metal contamination:

- employ a lower electric field within the p-n junction depletion region to attenuate the band-to-band tunneling and field-enhanced generation of carriers, thus making it possible to reduce more effectively the DCR by cooling the detector.

Dedicated silicon fabrication technologies provide to the device designer the quality and flexibility necessary for attaining further improvements requested by the users. In the following the performance of the large-area SPAD devices recently fabricated will be reviewed, pointing out the most significant improvements.

## Review of Si-SPAD performance

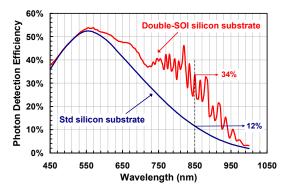

Fig. 1 shows the PDE of Si-SPAD devices as a function of wavelength, measured at 5 V excess bias voltage. Devices built in standard double-epitaxial silicon substrates have a peak PDE of 52% at 550 nm, whereas the PDE at 850 nm wavelength is still about 12%. Resonant-cavity-enhanced SPAD fabricated on a double silicon-on-insulator (SOI) substrate have peak photon detection efficiencies ranging from 42% at 780 nm to 34% at 850 nm. It has been verified that the PDE is independent of the SPAD diameter.

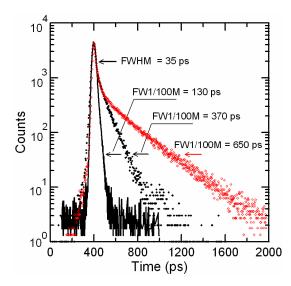

Fig. 2 (diamonds) shows the time response of a 200 µm SPAD detector to an ultrafast laser diode emitting 10 ps FWHM optical pulses at 820-nm wavelength. Thanks to the use of a patented pick-off circuit designed for extracting the time information from the avalanche current pulse [9, 10], a timing jitter of 35 ps FWHM was obtained at 5 V excess bias voltage, not dependent on the size of the SPAD active area. The curve shows a clean exponential diffusion tail with a

time constant of 280 ps. Fig. 2 (dots) can be taken as a clear example of advantage provided by a fully custom SPAD technology. By simply reducing the thickness of neutral layer beneath the active junction, a reduction of the tail lifetime from 280 to 110 ps is obtained. The diffusion tail can be completely eliminated by exploiting fully-depleted SPAD structure (Fig. 2, continuous line) [7].

Figure 1: Photon detection efficiency as a function of wavelength for SPAD detectors having standard and double-SOI substrate.

Figure 2: Time response of three different 200-µm SPAD detector devices to a picosecond laser pulse at 820 nm. The diffusion tail length is reduced by reducing the neutral silicon layer beneath the active junction.

Table I summarize the typical values of DCR and total afterpulsing probability measured with Si-SPADs having different diameter. The devices were operated at -15°C by using a Peltier thermoelectric cooler. Measurements were performed at 5 V excess bias voltage by using an integrated active quenching circuit (i-AQC) with a dead time of 80 ns [11]. The performance reported in Table 1 is remarkable, showing that 100 µm diameter devices can be reliably

achieved with DCR of about 100 c/s and total afterpulsing probability lower than 2%.

| SPAD Diameter | DCR@-15°C | Afterpulsing probability @-15°C |

|---------------|-----------|---------------------------------|

| 50 μm         | < 20 c/s  | 1.4%                            |

| 100 µm        | 100 c/s   | 1.8%                            |

| 200 μm        | 2000 c/s  | 3.0%                            |

Table1: DCR and the total afterpulsing probability measured at 15°C with Si-SPADs having different diameter

Based on this technology, we have developed a compact (5cmx4cmx8cm) counting/timing module that is now commercially available.

### Conclusions

We developed a dedicated silicon fabrication technology capable of providing the quality and flexibility necessary for attaining the performance required in QKD applications. In particular, there is realistic prospect of commercial development of SPADs with diameter larger than 100 µm, high photon detection efficiency in visible range and excellent timing resolution. To achieve this objective we combined different strategies including ultra-clean fabrication process, specific gettering procedures, electric field profile engineering, and low-level detection of the avalanche current leading edge. Compact photon counting modules exploiting the SPAD devices reported here have been efficiently used in GHz-clocked QKD at both 850 nm (direct detection) [12] and 1.55 µm (frequency upconversion) [5, 6].

## References

- P. D. Townsend, IEEE Phot. Techn. Lett. 10 (1998), 1048.

- K. J. Gordon et al., IEEE J. Quant. Elect. 40 (2004), 900.

- 3. J. C. Bienfang et al, Opt. Exp. 12 (2004), 2011.

- 4. K. J. Gordon et al, Opt. Exp. 13 (2005), 3015.

- 5. R. T. Thew et al, New J. Phys. 8 (2006), 32.

- 6. H. Takesue et al, Opt. Exp. 14 (2006), 9522.

- 7. M. Ghioni et al, IEEE J. Sel. Topics in Quantum Electronics 13 (2007), 852.

- M. Ghioni et al, Proc. of SPIE, Vol. 6900 (2008), 69001D.

- S. Cova et al, US patent No. 6,384,663 B2, May 7, 2002.

- 10. A. Gulinatti et al, Electron.Lett., 41 (2005), 272.

- 11. F. Zappa et al, IEEE J. Solid-State Circuits 38 (2003), 1298.

- 12. J. C.Bienfang et al, Proc. of SPIE Vol. 6780 (2007), 67800C.